ВНИМАНИЕ!

Этот «кусок» фирменного описания был переведен не на заказ, а для лучшего

понимания принципов работы (для внутреннего потребления). Ошибок перевода

(принципиальных и мешающих осмыслению) не замечено. Если такие найдутся, то ICQ:213-937-192.

Проект не коммерческий. Распространяется КАК ЕСТЬ. Впервые выложен на

http://www.tasek.nm.ru/ 10 апреля 2006 года.

Analog-to-Digital

Converter

Техническая Характеристика

· Разрешение 10-бит

· Нелинейность ±0.5 LSB

· Абсолютная Погрешность ± 2 LSB

· Время Преобразования 13 - 260 µs

· Не более 15 kSPS при

Максимальном Разрешении

· Один из 6 Переключаемых Каналов

· Еще 2 Канала (TQFP and MLF Package only)

· Возможность выравнивания результата в левую

сторону

· 0 - VCC ADC Диапазон

входного напряжения

· Подключаемое 2.56V ADC Опорное

Напряжение

· Режимы Непрерывного (Free Running) и Единичного

преобразования (Single Conversion)

· Прерывание по окончании преобразования ADC

· Шумоподавитель в Спящем режиме

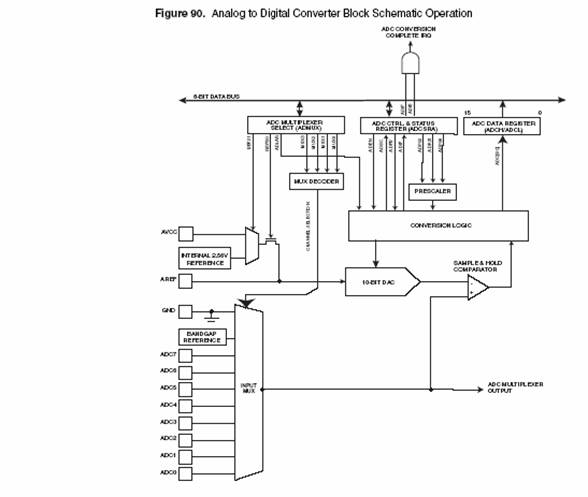

ATmega8 имеет 10-bit ADC последовательного приближения. ADC подключен к 8-ми канальному Аналоговому Мультиплексору

который позволяет подключить вход ADC к любому из восьми входов

(выводу Port C). Входы АЦП, при отсутствии входного напряжения, принимают

значение 0V (GND).

ADC содержит блоки выборки и хранения,

для запоминания входного напряжения на время преобразования. Функциональная

схема ADC показана на Figure 90.

ADC имеет отдельный вывод питания, AVCC. Напряжение питания ADC (вывод AVCC) не должно отличаться от VCC более чем на

± 0.3V. Как подключить этот вывод, смотри в разделе

"ADC компенсатор

шума" на странице 198.

Встроенный источник опорного напряжения

имеет номинальное напряжение 2.56V или

AVCC, при условии, что внутренний ИОН «включен». ИОН может быть «стабилизирован»

путем подключения к выводу AREF конденсатора

(на GND), для уменьшения шума.

ADC преобразует входное аналоговое

напряжение в 10-bit цифровое значение применяя последовательное

приближение. Минимальное значение соответствует уровню (напряжению) GND, а максимальное соответствует напряжению на выводе AREF минус 1 LSB (бит

младшего разряда). При необходимости, AVCC или

внутренний ИОН (2.56V) могут быть подключены к AREF. Для этого надо записать биты REFSn в регистре ADMUX. Внутренний

ИОН должен фильтроваться конденсатором на выводе AREF для уменьшения шума.

Подключение выбранного входного канала

производится записью битов MUX в регистре ADMUX. Каждый вход

ADC, измеряющий напряжение в диапазоне от GND до напряжения ИОН, должен быть

определен как одиночный вход ADC. Это определяется битами ADEN в регистре ADCSRA. Выбор источника ИОН и входа ADC не будет

иметь значения до тех пор, пока не установлен ADEN. ADC не подключен (не потребляет мощности)

когда бит

ADC возвращает 10-bit результат, который располагается в ADC регистрах данных, ADCH и ADCL. По умолчанию, имеющийся

результат выравнивается (сдвигается) в правую сторону (прим.пер.

для 10 битного преобразования), но результат может выравниваться и в левую сторону(прим.пер. для 8 битного преобразования, два младших

бита отбрасываются, теряются),

если установлен бит ADLAR регистра ADMUX.

Если результат выравнивается влево и

требуется не более 8-бит, то достаточно прочесть регистр ADCH. В других случаях, сначала должен быть прочитан регистр ADCL, а затем ADCH, пока не будет прочитан ADCH содержание Data Registers не

изменится и будет соответствовать тому же самому преобразованию. Как только начинается

чтение ADCL, доступ ADC к Data Registers блокируется. Это означает, что если преобразование ADC происходит после чтения ADCL, и завершается

до прочтения ADCH, то ни какой регистр (прим.пер. ADCL и ADCH) не изменит свое значение и результат

преобразования будет потерян. Когда чтение ADCH заканчивается, доступ ADC к регистрам ADCH и

ADCL возобновляется.

ADC имеет собственное прерывание, которое

может быть вызвано когда преобразование завершается. Когда доступ ADC к Data Registers запрещен

между чтением ADCH и ADCL, прерывание будет вызвано даже если результат преобразования

потерян.

Запуск преобразования

Одиночное преобразование начинается когда

записывается логическая единица в ADC Start Conversion bit, ADSC. Этот бит

остается в состоянии логической единицы в течение всего преобразования и

аппаратно сбрасывается когда преобразование завершено. Если, во время преобразования,

выбран другой входной канал, то ADC завершит текущее

преобразование перед переключением на новый канал.

В режиме Непрерывной Работы ADC постоянно производит выборку и

обновляет Data Register. Режим Непрерывной Работы выбирается установкой бита ADFR в ADCSRA. Запуск

преобразования, в этом режиме, происходит после установки бита ADSC в ADCSRA. В этом

режиме ADC производит преобразование

(последовательное приближение) независимо от того, установлен ли флаг

прерывания или нет, т.е. бит ADIF очищен

или нет.

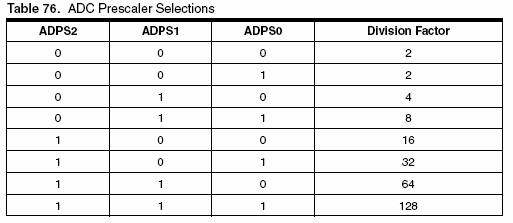

Предделитель и время преобразования

По умолчанию, последовательное приближение производится

на частотах от 50 кГц до 200 кГц, при максимальном разрешении. Если необходимо разрешение

менее 10 бит, то частота преобразования может быть более 200 кГц, для получения

более высокой скорости преобразования.

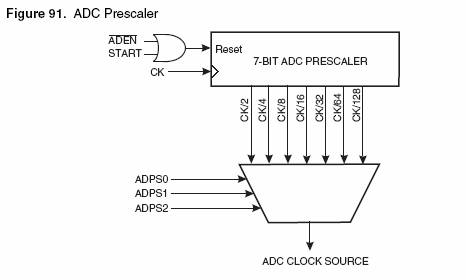

ADC содержит предделитель, который формирует

допустимую частоту преобразования из любой частоты CPU, если она

более 100 kHz. Предделитель устанавливается битами ADPS в ADCSRA. Предделитель

начинает работать когда, установкой бита ADEN в ADCSRA, включается ADC. Предделитель работает все время пока установлен бит ADEN, и сбрасывается когда ADEN равен нулю.

Когда запущено одиночное (разовое)

преобразование, путем установки бита ADSC в

ADCSRA, преобразование начинается по первому положительному (из 0

в 1) фронту ADC clock cycle. Нормальное

преобразование

длится 13 тактов

частоты ADC clock cycles. Первое преобразование

после включения ADC (установка бита ADEN в

ADCSRA) требует 25 тактов ADC clock cycles для инициализации

аналоговой части.

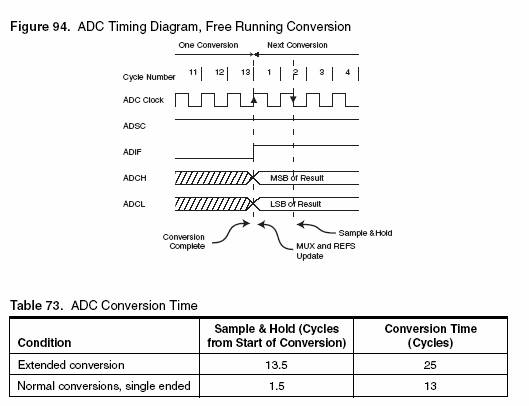

Фактическая выборка и запоминание входного

стгнала происходит в течение 1.5 тактов ADC clock cycles после начала при обычном преобразовании и в течение 13.5 тактов

ADC clock cycles после

начала при первоначальном включении. Когда преобразование завершено, результат

записывается в ADC Data Registers, и устанавливается бит ADIF. В режиме разового

преобразования, бит ADSC сбрасывается одновременно с установкой

ADIF. Программно бит ADSC может

бить установлен снова, и новое преобразование начнется по первому

положительному фронту ADC clock.

В режиме Free Running, новое преобразование начинается

сразу же по завершении предыдущего преобразования, пока бит ADSC остается высоким. Время преобразования

в различных режимах показано в Table 73.

Выбор канала или источника опорного

напряжения

Биты MUXn и REFS1:0 в регистре ADMUX являются единственными

буферизированными через временный регистр, к которому CPU имеет произвольный доступ. Это гарантирует, что изменение входного

канала и источника опорного напряжения будет происходить только в безопасный

момент преобразования (по окончании одного и до начала следующего

преобразования). Изменение канала и ИОН может быть проведено в любой момент до

начала преобразования. После начала преобразований (с приходом первого

импульса) выбор канала и ИОН запрещается на время всего преобразования. Продолжение

выбора канала и ИОН начинается в последнем цикле ADC clock cycle перед завершением преобразования (когда

бит ADIF в ADCSRA устанавливается). Учтите, что преобразование

начинается по переднему (положительному) фронту ADC clock после

того, как бит ADSC установлен.

Тем самым, изменение канала и ИОН в регистре ADMUX не может быть произведено, пока не пройдет один импульс ADC clock после установки бита ADSC.

Если установлены биты ADFR и ADEN, то

прерывание по окончанию преобразования может происходить в любое время. Если регистр

ADMUX изменен во время обработки

прерывания, то не возможно определить с какими настройками (прежними или

новыми) будет произведено следующее преобразование. Содержание регистра ADMUX должно изменяться при следующих

условиях:

1. Когда

бит ADFR или ADEN сброшен.

2. В течение преобразования, по прошествии

минимум одного цикла ADC clock после установки бита окончания

преобразования.

3. После

окончания преобразования, но перед тем как будет сброшен флаг прерывания (ИМХО

до окончания обработки прерывания).

Если изменение содержимого регистра ADMUX произведено с соблюдением одного из этих условий, то

следующее преобразование будет проведено с учетом новых установок.

Входные каналы ADC

При выборе входного канала необходимо следить

за тем, что выполнены следующие условия правильного выбора канала:

При одиночном преобразовании

выбор канала всегда производится перед началом преобразования. Выбор другого канала

может быть произведен, не ранее чем, в первый цикл ADC clock после

установки бита ADSC. Однако, самый простой метод – это

ждать окончания преобразования, а затем выбирать (изменять) входной канал.

В режиме Непрерывной работы канал

всегда выбирается до начала первого преобразования. Выбор другого канала может быть

произведен, не ранее чем, в первый цикл ADC clock после установки бита ADSC. Однако, самый простой метод – это ждать окончания преобразования,

а затем выбирать (изменять) входной канал. Так как следующее преобразование уже

началось автоматически, то его результат отразит предыдущий выбор канала. Последующие

преобразования отразят новый выбор канала.

Источник опорного напряжения ADC

Опорное (образцовое) напряжение ADC (VREF) определяет диапазон преобразования

ADC. Если, измеряемое напряжение превышает VREF, то результатом одиночного преобразования будет значение 0x3FF. VREF может быть выбран как напряжение AVCC, встроенный

ИОН 2.56V, или внешний источник, подключенный к

выводу AREF.

AVCC соединен с ADC через пассивный переключатель. Встроенный ИОН 2.56V состоит из внутреннего стабилизатора (VBG) и встроенного усилителя. В любой микросхеме ATmega8, внешний вывод AREF подсоединен

непосредственно к ADC, и стабильность внутреннего ИОН

может быть увеличена путем подключения блокировочного конденсатора между

выводом AREF и общим

проводом. Напряжение VREF может

быть измерено вольтметром в высоким входным сопротивлением на выводе AREF. Помните, что измерять VREF можно только вольтметром с высокоомным входом, и только при

подключенном блокировочном конденсаторе.

Если используется внешний источник опорного напряжения, который подсоединен

к выводу AREF, то использовать внутренние ИОН (AVCC или 2.56V) невозможно,

так как они будут зашунтированы внешним напряжением. Если внешний ИОН не подключен

к выводу AREF, то в качестве ИОН используется или

AVCC или 2.56V. Первое,

после выбора нового ИОН, преобразование может быть неточным, поэтому его

следует не учитывать (пропускать).

ADC шумоподавитель

ADC имеет шумоподавитель, который обрабатывает

преобразование в спящем режиме, для устранения помех, создаваемых CPU и периферийными устройствами. Шумоподавитель может использоваться и в режиме Idle (пониженного энергопотребления). Для использования шумоподавителя необходимо выполнить следующее:

1. ADC должно бить разрешено и не занято преобразованием. Должен быть

выбран режим одиночного преобразования и разрешено прерывание по окончанию

преобразования.

2. Установите режим Уменьшения Шума

ADC (или режим Idle). ADC начнет преобразование только когда

будет остановлен CPU.

3. Если никакие другие прерывания

не произойдут до момента завершения преобразования ADC, то

прерывание от ADC «разбудит» CPU, который перейдет

на обработку этого прерывания. Если другое прерывание «пробуждает» CPU до завершения преобразования ADC, то будет выполнено это (разбудившее) прерывание, и запрос на

прерывание от ADC будет сгенерирован по окончании

преобразования. CPU останется в

активном режиме пока не получит новую команду на остановку (sleep command is executed).

Помните, что ADC не выключится автоматически при новой остановке CPU в режиме Idle и режиме Уменьшения Шума. Для остановки ADC необходимо сбросить бит ADEN перед переходом в спящий режим, для того чтобы избежать

потребления мощности ADC.

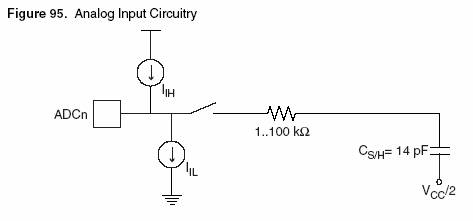

Схема Аналогового Входа

Схема аналогового входа для одиночного

канала показана на Figure 95. Каждый аналоговый вход ADCn, имеет внутренний резистор и конденсатор, во всех каналах ADC. Когда канал подключен, к источнику сигнала подключается резистор

и конденсатор S/H (комбинированное

сопротивление).

ADC оптимизирован для аналоговых сигналов

с полным выходным сопротивлением не более 10 кОм. При этом время выборки

(преобразования) будет небольшим. Если источник обладает более высоким сопротивлением,

то время преобразования будет определятся временем заряда (от источника)

конденсатора S/H, и может

меняться в широких пределах. Рекомендуется использовать источники сигнала с низким

выходным сопротивлением и медленно изменяющимися сигналами, так как это

минимизирует время перезаряда конденсатора S/H.

Изменение входного сигнала с частотой выше

чем Nyquist (fADC/2) недопустимо,

так как может привести к непредсказуемым искажениям при преобразовании. Рекомендуется

удалять высокочастотные составляющие сигнала путем установки ФНЧ на входе ADC.

Методы(способы) Шумоподавления

Цифровая часть устройства как внутри, так и

снаружи генерирует EMI (электро -

магнитные импульсы), которые могут воздействовать на точность аналоговых

значений. Если точность преобразования аналогового сигнала критична, то уровень

шума может быть снижен следующими методами:

1. Проводники (дорожки на плате)

аналогового сигнала должны быть максимально короткими.

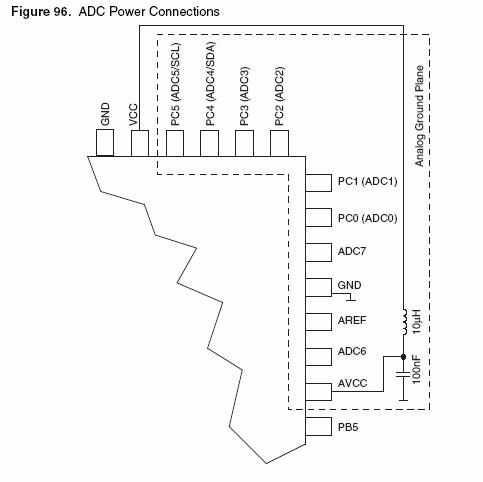

2. Вывод AVCC должен быть соединен с выводом VCC через LC фильтр,

как показано на Figure 96.

3. Используйте функцию

Шумоподавления для уменьшения помех от CPU.

4. Если любой из выводов портов ADC [3..0] используется как цифровой выход, то необходимо чтобы

он (они) не переключались во время преобразования входного аналогового сигнала.

Однако, использование Two-wire Interface (I2C) (ADC4 и ADC5) будет

воздействовать только на преобразование на выводах ADC4 и ADC5 и не влияет на другие каналы ADC.

Точность преобразования ADC

Одиночное, n-битное преобразование

ADC переводит величину входного напряжения

в диапазоне от GND до VREF линейно за 2n шагов (LSBs). Самый низкий код читается

как 0, а самый высокий как 2n-1.

Отдельные параметры описывают отклонение

преобразователя от идеального:

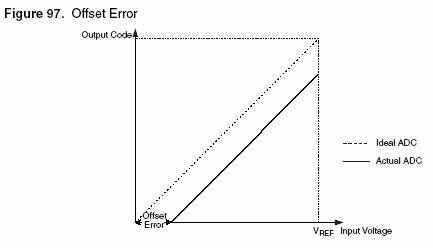

· Начальное Смещение: Отклонение первого (начального)

перемещения (итерации) (0x000 to 0x001) сравниваемое с идеальным перемещением (0.5 LSB). Идеальное значение: 0 LSB.

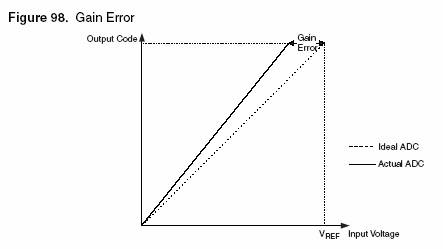

· Ошибка Усиления: После корректировки Начального

Смещения, Ошибка Усиления определяется как отклонение последнего перемещения

(итерации) (0x3FE к 0x3FF) от идеального

перемещения (в 1.5 LSB ниже

максимума). Идеальная величина: 0 LSB

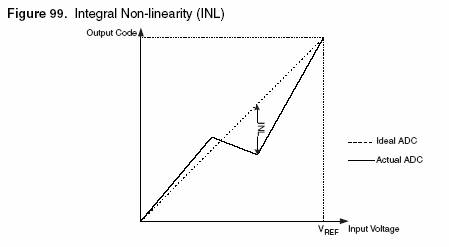

· Интегральная Нелинейность(INL): После корректировки Начального Смещения и Ошибки Усиления, INL это максимальное отклонение фактического

перемещения, сравниваемого с идеальным перемещением для любого участка. Идеальная

величина: 0 LSB.

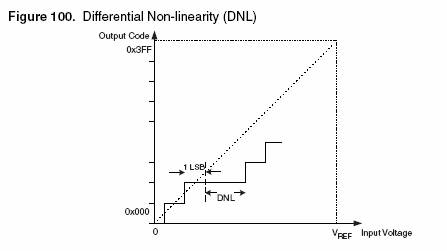

· Дифференциальная Нелинейность (DNL): Максимальное отклонение фактической ширины кода (в интервале

между двумя смежными приращениями) от идеальной ширины кода (1 LSB). Идеальная величина: 0 LSB.

· Ошибка квантования: Из-за того, что входное напряжение преобразуется в конечное число кодов, минимальное и максимальное значение входного напряжения , в диапазоне единицы квантования (1 LSB), будет иметь одно и то же значение. Ошибка квантования всегда равна ±0.5 LSB.

· Абсолютная

точность: Абсолютная точность – это максимальное отклонение фактического

(нескорректированного) приращения (итерации), которое сравнивается с идеальным

перемещением. Это обобщенная ошибка Начального Смещения, Ошибки Усиления, Интегральной

Нелинейности, Дифференциальной Нелинейности, Ошибки квантования. Идеальная величина: ±0.5 LSB.

Результат Преобразования ADC

После окончания преобразования (установлен бит

ADIF), результат этого преобразования находится в ADC Result Registers (ADCL, ADCH).

Для единичного преобразования результат

определяется как –

где VIN – напряжение

на выбранном выводе и VREF выбранное

опорное напряжение (смотри Table 74 на странице 203 и Table 75 на странице 203). 0x000 соответствует

напряжению общего провода (GND), и 0x3FF соответствует

напряжению ИОН минус один разряд LSB.

Переключение Мультиплексора ADC

Регистр ADMUX

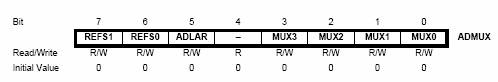

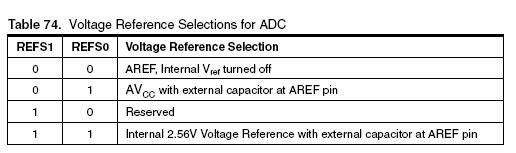

· Биты

7:6 REFS1:0: Биты

выбора ИОН

Этими битами выбирается

ИОН для ADC в соответствие

с Table 74. Если эти биты изменены пока идет преобразование, то

изменение вступит в силу после окончания текущего преобразования (установиться

бит ADIF в ADCSRA). Внутренний (встроенный) ИОН не может быть использован

если к выводу AREF подключен внешний ИОН.

· Bit 5 ADLAR: Выравнивание

результата в левую сторону

Бит ADLAR воздействует на результат преобразования, находящийся в ADC Data Register. Установите бит ADLAR для левого выравнивания результата.

Иначе, результат выравнивается вправо. Изменение бита ADLAR будет воздействовать на ADC Data Register немедленно, независимо от любых

продолжающихся преобразований. Полное описание действия этого бита приводиться

в разделе "The ADC Data Register ADCL and ADCH" на странице 205.

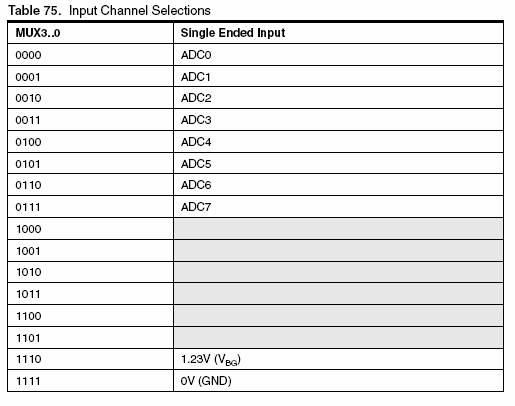

· Bits 3:0 MUX3:0: Переключение

Аналоговых Каналов (Входов)

Установкой этих битов выбирается вход,

подключаемый к ADC. Для выяснения деталей смотри Table 75. Если эти биты изменены в течение преобразования, то

изменение не будет иметь силы пока текущее преобразование не завершится

(устанавливается бит ADIF в

ADCSRA).

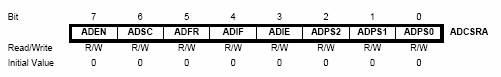

ADC Управление и Состояние

Регистр A ADCSRA

· Бит

7

Установка этого бита включает ADC. А сброс этого бита выключает ADC. Переключение

ADC во время преобразования приведет к

завершению этого преобразования.

· Бит 6 ADSC: ADC Старт Преобразования

В режиме одиночных преобразований

установка этого бита приведет к началу следующего (каждого) преобразования. В

режиме непрерывного преобразования установка этого бита приведет к старту

первого преобразования. Первое (начальное) преобразование после установки бита ADSC которая (установка) произошла после

включения ADC, или если бит ADSC устанавливается одновременно с

включением ADC, займет (преобразование) 25 циклов ADC clock вместо 13 в нормальном режиме. Это первое (начальное) преобразование

выполняет инициализацию ADC.

ADSC будет читаться

как единица пока преобразование не завершено. При завершении преобразования этот бит сбрасывается аппаратно. Запись нуля в этот бит не будет иметь эффекта.

· Бит

5 ADFR: ADC Выбор

режима Непрерывного Преобразования

Когда установлен этот бит, то ADC переходит в режим Непрерывного Преобразования. В этом режиме преобразование

и запись результата в Data Registers происходит постоянно. Сброс

этого бита выключает режим Непрерывного Преобразования.

· Бит

4 ADIF: ADC Установка

прерывания

Этот бит устанавливается когда ADC преобразование завершении и результат

записан в Data Registers. Прерывание ADC обрабатывается

если биты ADIE и I-бит в регистре SREG установлены.

Бит ADIF очищается аппаратно

когда заканчивается обработка прерывания по вектору прерывания. Можно сбросить этот

бит, записав в него (to the flag) единицу.

Будьте внимательны при проведении цикла Чтение-Модификация-Запись регистра ADCSRA, так как может быть сброшено отложенное прерывание. Это(сброс

отложенного прерывания) так же актуально при использовании команд SBI CBI.

· Бит

3 ADIE: ADC Разрешение

прерывания

Когда этот бит установлен, и установлен

бит I регистра SREG, прерывание по завершению преобразования ADC разрешено.

· Биты

2:0 ADPS2:0: ADC Выбор

частоты предделетеля

Эти биты определяют соотношение между

тактовой частой процессора и частотой дискретизации ADC.

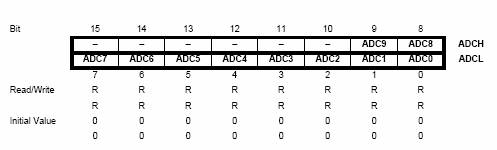

Регистры данных ADC

ADCL and ADCH

ADLAR = 0

ADLAR = 1

Когда преобразование завершено, результат находится в этих двух

регистрах.

Когда читается регистр ADCL, ADC Data Register не будет изменятся пока не будет прочитан ADCH. Следовательно, если результат выравнивается влево и требуется

8-ми разрядная точность, то достаточно читать ADCH. Иначе сначала

должен читаться ADCL, а затем ADCH.

Бит ADLAR в

регистре ADMUX, и биты MUXn в регистре ADMUX определяют

способ, которым считывается результат. Если ADLAR установлен, то результат выровнен влево. Если бит ADLAR сброшен (по умолчанию), то

результат выровнен вправо.

· Биты ADC9:0: ADC Результат преобразования

В этих битах находится результат

преобразования, детально они рассмотрены в главе "ADC Результат преобразования" на странице 202.